目录

1.GaN 栅极驱动考虑因素 – 引言

2.GaN 栅极驱动考虑因素 – 设计指南

3.栅极驱动器电路示例(请登录或注册)

a. 应用示例:隔离电源开关(请登录或注册)

b. 应用示例:半桥功率级(请登录或注册)

c. 应用示例:无桥 PFG(请登录或注册)

4.结论(请登录或注册)

GaN 栅极驱动考虑因素 – 引言

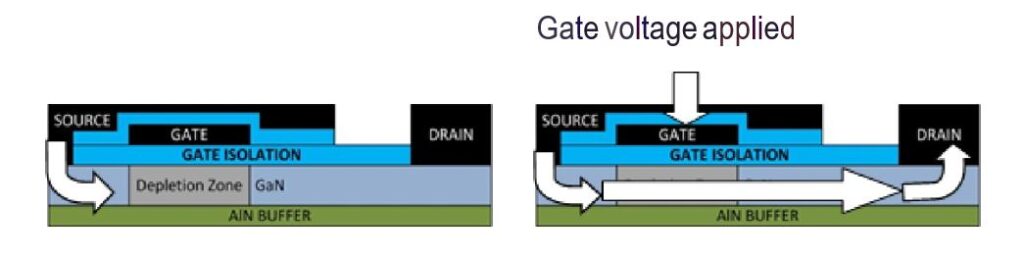

氮化镓 (GaN) 半导体是高电子迁移率晶体管 (HEMT) 器件,这是一类具有近乎完美开关特性的晶体管。HEMT 意味着电子以二维电子气形式和极高的电子迁移率在内部晶体结构中运动,进而产生导电性极高、RSDON 较低的器件。GaN 化学物质的使用增大了击穿电压,这意味着晶体管内的各个层可以做得非常薄且紧密。这既能加快开关速度,又能减少栅极电容。

增强型 (E-HEMT) 晶体管在栅极下有一个耗尽层,该层会阻止电子流动,并且需要相对于源极引脚的正栅极电压才能导通。由于栅极下的耗尽层非常薄,只需注入非常少的电荷就可以使晶体管导通和关断,因此在不产生高开关损耗的情况下,开关速度可以达到 MHz 频率级别。

图 1:增强型 GaN 晶体管在“关断”和“导通”状态下的示意图

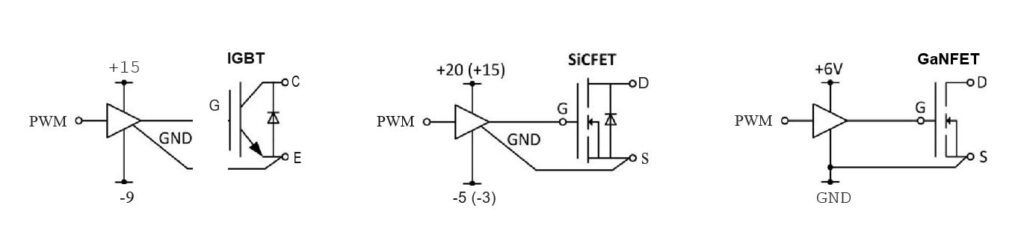

极薄的栅极隔离层意味着高栅极-源极电压将导致内部闪络,即使材料本身具有很高的击穿电压额定值也会如此。GaN E-HEMT 的典型全增强电压为 7 V,但是,如果 VGS 超过 ±10 V(远低于 IGBT 或 SiC 栅极驱动器中通常使用的栅极电压),则会造成损坏。由于低电容栅极沟道的上升和下降时间极快,因此外部栅极驱动中任何过大电感都可能导致电压尖峰或电压振铃,进而超过这些电压限值。因此,6V 栅极驱动电压是一种良好的折中,既能保持高效率,又能处于安全工作区域内。

IGBT 或 SiC 栅极驱动电路通常也在负栅极驱动电压下关断。这有助于加快从栅极电容中提取电荷的速度,从而缩短了关断时间。GaN 晶体管的栅极电容低到不需要负栅极驱动电压。OV 的栅极电压可在几纳秒内可靠地完全关断 HEMT。只有在布局中包含过大电感时,负栅极驱动才能提供保护,防止由于振铃引起的意外导通。但是,由于 HEMT 没有像 MOSFET 那样的体二极管,而且是对称导电器件,因此负栅极电压会增加反向导通损耗。单端 6 V – 0 V 的栅极驱动电压是理想选择。

图 2 显示了常用的典型栅极驱动器电压。第一代 SiC MOSFET 使用 +20/-5 V 电源电压,但第二代器件最有可能使用 +15/-3 V 电源电压:

图 2:IGBT、SiC 和 GaN 驱动器的典型栅极驱动器电源电压

2.GaN 栅极驱动考虑因素 – 设计指南

1:大多数超快栅极驱动器 IC 具有欠压锁定 (UVLO) 功能,此功能会在电源电压过低时禁用输出。用于 IGBT/SiC 应用的器件通常具有相对较高的 UVLO 电压,因为其工作电源电压最高可达 24 V。必须选择与 GaN 中低得多的栅极电压兼容的栅极驱动器。

2:对栅极电容充电和放电所需的电流取决于栅极电容和栅极电压的变化率。尽管 GaN 栅极电容非常低,但高电压变化率 (dv/dt) 意味着栅极驱动器至少需要 ±0.5 A(1 A 灌电流更好)的电流驱动能力。此峰值电流将由尽可能靠近驱动器引脚安装的陶瓷电容提供,因此平均电源电流会大大降低(数十毫安范围内)。栅极驱动器的灌电流驱动应当为低阻抗(<2 Ω)以减少跨导的几率(见下一条注释)。

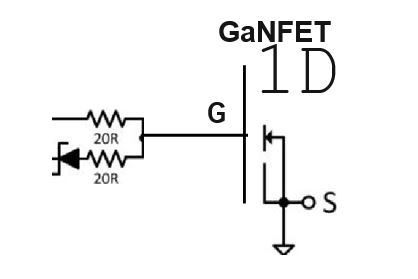

3:由于栅极驱动器寄生电感与高米勒电容放电电流相互作用,超快栅极驱动设计容易受到不良导通(跨导)的影响,从而产生振铃振荡,导致栅极电压瞬间再次升高。压摆率可以通过 dv/dt 限制电阻来限制,以降低这种效应的可能性。10-20 Ω 范围内的导通栅极电阻通常会产生 80-40 kV/µs 的压摆率。关断阻抗应该更小以减少关断损耗。可以使用与栅极电阻并联的肖特基二极管和电阻来独立控制导通和关断压摆率(图 3)。

图 3:使用栅极电阻控制压摆率

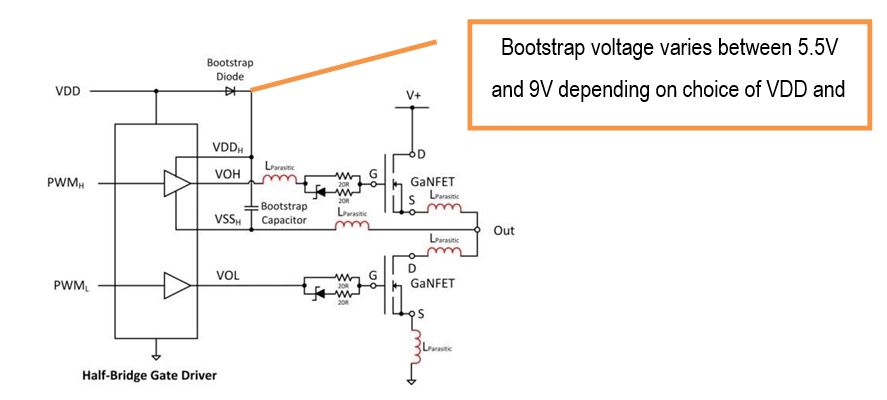

4:高侧栅极驱动器通常采用自举电源电路实现(图 4)。尽管这意味着高侧和低侧驱动器可以使用同一个隔离电源,但仍存在一些固有缺点。

例如,自举二极管必须具有超快恢复特性。如果它的关闭速度达不到 GaN 输出的水平,那么反向电流将流回 VDD 电源端。这些电流尖峰不仅会影响二极管的寿命,还会对电源轨造成高频干扰,从而严重影响 EMC 合规性。

栅极驱动器自举电源电压取决于 VDD 电源电压与电容耦合输出(开关节点)电压之差。这意味着在工作期间,自举电容两端的电压变化可能超过 ±20%。

高压自举二极管两端大约有 0.8-1.0 V 的压降,这意味着需要 7 V 电源电压来提供所需的 6 V 驱动电压 (VDDH)。但是,开关节点电压在正向导通期间最高可达 +0.5 V,这意味着有效的栅极驱动器电源电压只有 5.5 V。如果栅极驱动器电源电压过低,GaN HEMT 将无法实现完全增强,而且导通损耗也更高。在突发模式下或者在导通后的初始脉冲期间,这种条件尤其关键,因为第一个脉冲狭窄,自举电容可能无法充满电。

但是,不建议将电源电压提高到 7.5 V 来保证最小 6 V 的 VDDH 电压,因为在反向导通条件下,开关节点电压可以反弹至低于地电压的 -2.5 V,这意味着有效自举电压变为 +6.5 V +2.5 V = 9 V。这已经十分接近 10 V 的绝对最大栅极电压值。与负载电流和寄生电感的相互作用还会导致开关节点因高 di/dt 跳变而产生负向尖峰,从而导致自举电压的工作条件超过 10 V(如果将这些瞬变也考虑在内)。

图 4:显示了有害寄生电感的典型高侧自举电源电路